#### 4-OUTPUT LOW POWER FANOUT BUFFER FOR PCIE GEN3 AND 10G ETHERNET IDT6V31021

### **General Description**

The IDT6V31021 is a 4-output low- power differential buffer. Each output has its own OE# pin. It has a maximum operating frequency of 167 MHz and supports all SERDES clock frequencies for Freescale QorIQ CPUs.

# **Recommended Application**

PCIe Gen1/2/3 or Ethernet Fanout Buffer, or any application requiring low additive phase jitter.

# **Output Features**

- 4 low power differential output pairss

- Individual OE# control of each output pair

#### **Features/Benefits**

- Low power differential outputs; power efficient

- Power down mode when all OE# are high; reduces system standby power

- Industrial temperature range; can be used in demanding environments

- 20-pin MLF; space savings

#### **Key Specifications**

- Output cycle-cycle jitter <15ps additive

- Output to Output skew: <50ps

- PCIe Gen3 addtive phasejitter <0.3ps rms

- 10.3125G/64 additive phase jitter <100fs rms

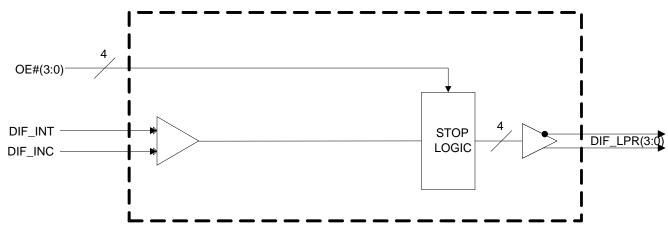

# **Block Diagram**

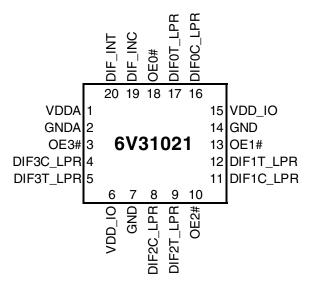

### **Pin Configuration**

20-pin MLF

#### **Power Connections**

| Pin Nur | nber (MLF) | Description           |

|---------|------------|-----------------------|

| VDD     | GND        | Description           |

| 6,15    | 7,14       | VDD_IO for DIF(3:0)   |

| 1       | 2          | 3.3V Analog VDD & GND |

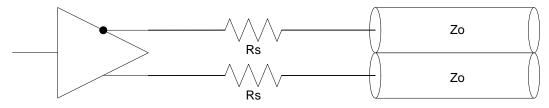

#### Terminations

Zo - 17 = Rs (ohms), where Zo is the single-ended intrinsic impedance of the board transmission line. Single-ended intrinsic impedance is  $\frac{1}{2}$  that of the differential impedance.

| Single Ended | Rs        |              |                             |

|--------------|-----------|--------------|-----------------------------|

| Impedance    | 5%        | Rs           |                             |

| (Zo)         | tolerance | 2% tolerance | Notes                       |

| 50           | 33        | 33.2         | In general, 5% resistors    |

| 45           | 27        | 27.4         | may be used. All values are |

| 42.5         | 24 or 27  | 24.9         | in ohms.                    |

# **Pin Descriptions**

| PIN # | PIN NAME  | <b>PIN TYPE</b> | DESCRIPTION                                                                                    |

|-------|-----------|-----------------|------------------------------------------------------------------------------------------------|

| 1     | VDDA      | PWR             | 3.3V Power for the Analog Core                                                                 |

| 2     | GNDA      | GND             | Ground for the Analog Core                                                                     |

| 3     | OE3#      | IN              | Output Enable for DIF3 output. Control is as follows:<br>0 = enabled, 1 = Low-Low              |

| 4     | DIF3C_LPR | OUT             | Complement clock of low power differential clock pair. (no 500hm shunt resistor to GND needed) |

| 5     | DIF3T_LPR | OUT             | True clock of low power differential clock pair. (no 50ohm shunt resistor to GND needed)       |

| 6     | VDD_IO    | PWR             | Power supply for low power differential outputs, nominal 1.05V to 3.3V                         |

| 7     | GND       | GND             | Ground pin                                                                                     |

| 8     | DIF2C_LPR | OUT             | Complement clock of low power differential clock pair. (no 50ohm shunt resistor to GND needed) |

| 9     | DIF2T_LPR | OUT             | True clock of low power differential clock pair. (no 50ohm shunt resistor to GND needed)       |

| 10    | OE2#      | IN              | Output Enable for DIF2 output. Control is as follows:<br>0 = enabled, 1 = Low-Low              |

| 11    | DIF1C_LPR | OUT             | Complement clock of low power differential clock pair. (no 50ohm shunt resistor to GND needed) |

| 12    | DIF1T_LPR | OUT             | True clock of low power differential clock pair. (no 50ohm shunt resistor to GND needed)       |

| 13    | OE1#      | IN              | Output Enable for DIF1 output. Control is as follows:<br>0 = enabled, 1 = Low-Low              |

| 14    | GND       | GND             | Ground pin                                                                                     |

| 15    | VDD_IO    | PWR             | Power supply for low power differential outputs, nominal 1.05V to 3.3V                         |

| 16    | DIF0C_LPR | OUT             | Complement clock of low power differential clock pair. (no 50ohm shunt resistor to GND needed) |

| 17    | DIF0T_LPR | OUT             | True clock of low power differential clock pair. (no 50ohm shunt resistor to GND needed)       |

| 18    | OE0#      | IN              | Output Enable for DIF0 output. Control is as follows:<br>0 = enabled, 1 = Low-Low              |

| 19    | DIF_INC   | IN              | Complement side of differential input clock                                                    |

| 20    | DIF_INT   | IN              | True side of differential input clock                                                          |

### **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the IDT6V31021. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| PARAMETER              | SYMBOL              | CONDITIONS                   | MIN       | TYP | MAX | UNITS | Notes |  |

|------------------------|---------------------|------------------------------|-----------|-----|-----|-------|-------|--|

| Maximum Supply Voltage | VDDA                | Core Supply Voltage          |           |     | 4.6 | V     | 1,7   |  |

| Maximum Supply Voltage | VDD_IO              | Low-Voltage Differential I/O | 0.99      |     | 3.8 | V     | 1,7   |  |

| Maximum Input Voltage  | V <sub>IH</sub>     | 3.3V LVCMOS Inputs           |           |     | 4.6 | V     | 1,7,8 |  |

| Minimum Input Voltage  | V <sub>IL</sub>     | Any Input                    | Vss - 0.5 |     |     | V     | 1,7   |  |

| Ambient Operating Temp | T <sub>ambIND</sub> | Industrial Range             | -40       |     | 85  | °C    | 1     |  |

| Storage Temperature    | Ts                  | -                            | -65       |     | 150 | °C    | 1,7   |  |

| Input ESD protection   | ESD prot            | Human Body Model             | 2000      |     |     | V     | 1,7   |  |

#### **Electrical Characteristics–Input/Supply/Common Output Parameters**

| PARAMETER                                                            | SYMBOL                  | CONDITIONS                                                                                                                     | MIN                   | TYP      | MAX                   | UNITS    | Notes   |

|----------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|-----------------------|----------|---------|

| Supply Voltage                                                       | VDDA                    | Supply Voltage                                                                                                                 | 3.000                 | 3.3      | 3.600                 | V        | 1       |

| Supply Voltage                                                       | VDDxxx_IO               | Low-Voltage Differential I/O<br>Supply                                                                                         | 0.99                  | 1.05-3.3 | 3.600                 | V        | 1       |

| Input High Voltage                                                   | V <sub>IHSE</sub>       | Single-ended inputs                                                                                                            | 2                     |          | V <sub>DD</sub> + 0.3 | V        | 1       |

| Input Low Voltage                                                    | V <sub>ILSE</sub>       | Single-ended inputs                                                                                                            | V <sub>SS</sub> - 0.3 |          | 0.8                   | V        | 1       |

| Differential Input High<br>Voltage                                   | V <sub>IHDIF</sub>      | Differential inputs<br>(single-ended measurement)                                                                              | 600                   |          | 1.15                  | V        | 1       |

| Differential Input Low<br>Voltage                                    | VILDIF                  | Differential inputs<br>(single-ended measurement)                                                                              | V <sub>SS</sub> - 0.3 |          | 300                   | V        | 1       |

| Input Slew Rate - DIF_IN                                             | dv/dt                   | Measured differentially                                                                                                        | 0.4                   |          | 8                     | V/ns     | 2       |

| Input Leakage Current                                                | I <sub>IN</sub>         | $V_{IN} = V_{DD}, V_{IN} = GND$                                                                                                | -5                    |          | 5                     | uA       | 1       |

| -                                                                    | I <sub>DD_3.3V</sub>    | VDDA supply current                                                                                                            |                       | 15       | 20                    | mA       | 1       |

| Operating Supply Current                                             | I <sub>DD_10_133M</sub> | VDD_IO supply @ fOP =<br>133MHz                                                                                                |                       | 12       | 20                    | mA       | 1       |

| Power Down Current<br>(All OE# pins High)                            | I <sub>DD_SB_3.3V</sub> | VDDA supply current, Input<br>stopped, OE# pins all high                                                                       |                       | 500      | 750                   | uA       | 1       |

|                                                                      | I <sub>DD_SBIO</sub>    | VDD_IO supply, Input<br>stopped, OE# pins all high                                                                             |                       | 100      | 150                   | uA       | 1       |

| Input Frequency                                                      | Fi                      | $V_{DD} = 3.3 V$                                                                                                               | 15                    |          | 167                   | MHz      | 2       |

| Pin Inductance                                                       | L <sub>pin</sub>        |                                                                                                                                |                       |          | 7                     | nH       | 1       |

| Innut Consolitones                                                   | CIN                     | Logic Inputs                                                                                                                   | 1.5                   |          | 5                     | pF       | 1       |

| Input Capacitance                                                    | C <sub>OUT</sub>        | Output pin capacitance                                                                                                         |                       |          | 6                     | pF       | 1       |

| OE# latency<br>(at least one OE# is low)                             | T <sub>OE#LAT</sub>     | Number of clocks to enable<br>or disable output from<br>assertion/deassertion of OE#                                           | 1                     | 2        | 3                     | periods  | 1       |

| Clock stabilization time<br>(from all OE# high to first<br>OE# low). | T <sub>STAB</sub>       | Delay from assertion of first<br>OE# to first clock out<br>(assumes input clock running<br>and device in power down<br>state)) |                       |          | 150                   | ns       | 1       |

| Tdrive_OE#                                                           | T <sub>DROE#</sub>      | Output enable after<br>OE# de-assertion                                                                                        |                       |          | 10                    | ns       | 1       |

| Tfall_OE#                                                            | T <sub>FALL</sub>       | Fall/rise time of OE# inputs                                                                                                   |                       |          | 5                     | ns       | 1       |

| Trise_OE#                                                            | T <sub>RISE</sub>       |                                                                                                                                |                       |          | 5                     | ns       | 1       |

|                                                                      | ANOUT BUFFER F          | OR PCIE GEN3 AND 10G ETHERN                                                                                                    | ET                    |          | 4 ID                  | T6V31021 | REV A 1 |

### AC Electrical Characteristics–DIF Low Power Differential Outputs

| PARAMETER                                                | SYMBOL                         | CONDITIONS                                  | MIN  | TYP  | MAX  | UNITS       | NOTES |

|----------------------------------------------------------|--------------------------------|---------------------------------------------|------|------|------|-------------|-------|

| Rising/Falling Edge Slew<br>Rate                         | t <sub>SLR</sub>               | Differential Measurement                    | 1.5  | 2.2  | 4    | V/ns        | 1,2   |

| Slew Rate Variation                                      | t <sub>SLVAR</sub>             | Single-ended Measurement                    |      | 13   | 20   | %           | 1     |

| Maximum Output Voltage                                   | V <sub>HIGH</sub>              | Includes overshoot                          |      | 783  | 1150 | mV          | 1     |

| Minimum Output Voltage                                   | V <sub>LOW</sub>               | Includes undershoot                         | -300 | -22  |      | mV          | 1     |

| Differential Voltage Swing                               | V <sub>SWING</sub>             | Differential Measurement                    | 1200 |      |      | mV          | 1     |

| Crossing Point Voltage                                   | V <sub>XABS</sub>              | Single-ended Measurement                    | 250  | 336  | 550  | mV          | 1,3,4 |

| Crossing Point Variation                                 | V <sub>XABSVAR</sub>           | Single-ended Measurement                    |      | 14   | 140  | mV          | 1,3,5 |

| Duty Cycle Distortion                                    | D <sub>CYCDIS0</sub>           | Differential Measurement,<br>fIN<=133.33MHz |      | 1.6  | 3    | %           | 1,6   |

| Additive Cycle-to-Cycle<br>Jitter                        | DIFJ <sub>C2CADD</sub>         | Differential Measurement,<br>Additive       |      | 2.1  | 7    | ps          | 1     |

| DIF[3:0] Skew                                            | DIF <sub>SKEW</sub>            | Differential Measurement                    |      | 19   | 50   | ps          | 1, 11 |

| Propagation Delay                                        | t <sub>PD</sub>                | Input to output Delay                       | 2.5  | 3.3  | 3.8  | ns          | 1     |

| Additive Phase Jitter -<br>PCIe Gen1                     | t <sub>phase_addPCIG1</sub>    | 1.5MHz < 22MHz                              |      | 1.6  | 6    | ps<br>Pk-Pk | 1,9   |

| Additive Phase Jitter -<br>PCIe Gen2 High Band           | t <sub>phase_add</sub> PCIG2HI | High Band is 1.5MHz to<br>Nyquist (50MHz)   |      | 0.1  | 0.3  | ps rms      | 1,9   |

| Additive Phase Jitter -<br>PCIe Gen2 Low Band            | t <sub>phase_add</sub> PCIG2LO | Low Band is 10KHz to<br>1.5MHz              |      | 0.5  | 0.8  | ps rms      | 1,9   |

| Additive Phase Jitter -<br>PCIe Gen3                     | t <sub>phase_addPCIG3</sub>    | 2MHz - 4MHz,<br>2MHz - 5MHz                 |      | 0.19 | 0.3  | ps rms      | 1,9   |

| Additive Phase Jitter<br>161.1328125MHz =<br>10.3125G/64 | t <sub>phase_add10G/64</sub>   | 12KHz to 100MHz                             |      | 60   | 100  | fs rms      | 1,10  |

Notes on Electrical Characteristics (all measurements use R<sub>S</sub>=33ohms/C<sub>L</sub>=2pF test load):

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> Slew rate measured through Vswing centered around differential zero

<sup>3</sup> Vxabs is defined as the voltage where CLK = CLK#

<sup>4</sup> Only applies to the differential rising edge (CLK rising and CLK# falling)

<sup>5</sup> Defined as the total variation of all crossing voltages of CLK rising and CLK# falling. Matching applies to rising edge rate of CLK and falling edge of CLK#. It is measured using a +/-75mV window centered on the average cross point where CLK meets CLK#.

<sup>6</sup> This figure refers to the maximum distortion of the input wave form.

<sup>7</sup> Operation under these conditions is neither implied, nor guaranteed.

<sup>8</sup> Maximum input voltage is not to exceed maximum VDD

<sup>9</sup> The 6V31021has no PLL, so the part itself contributes very little jitter to the input clock. But this also means that the 9DBL411 cannot 'de-jitter' a noisy input clock. Values calculated per PCI SIG and per Intel Clock Jitter tool version 1.6.6. For PCIe RMS figures, additive jitter is calculated by solving the following equation: Additive jitter = SQRT[(total jitter)^2 - (input jitter)^2]

<sup>10</sup> Calculated from Agilent E5052A phase noise machine.

<sup>11</sup> Mean value not including cycle-to-cycle jitter

### **Marking Diagram**

Notes:

- 1. "\*\*' is the lot sequence.

- 2. '\$' is the mark code.

- 3. 'YWW' is the year and week that the part was assembled.

- 4. 'G' denotes RoHS compliant package.

- 5. 'I' denotes industrial temperature range.

- 6. Bottom marking: country of origin if not USA.

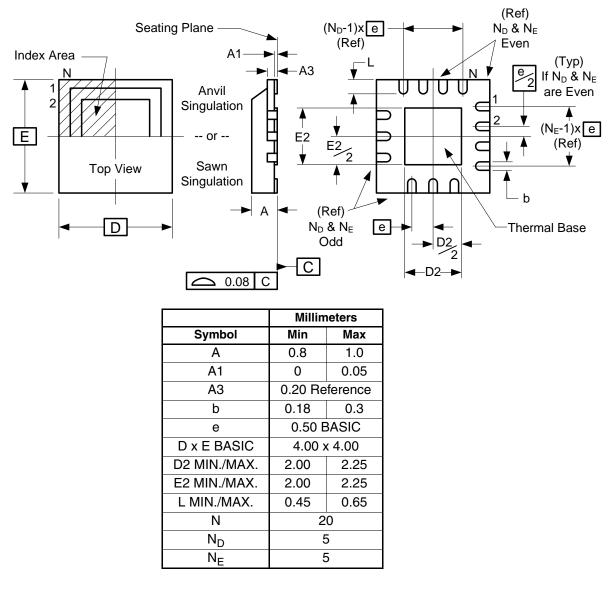

# Package Outline and Package Dimensions (20-pin MLF)

#### **Ordering Information**

| Part / Order Number | Shipping Packaging | Package    | Temperature  |

|---------------------|--------------------|------------|--------------|

| 6V31021NLGI         | Trays              | 20-pin MLF | -40 to +85°C |

| 6V31021NLGI8        | Tape and Reel      | 20-pin MLF | -40 to +85°C |

#### "G" after the two0letetr package code indicates Pb-Free configuration, RoHS compliant.

While the information presented herein has been checked for both accuracy and reliability, Integrated Device Technology (IDT) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are not recommended without additional processing by IDT. IDT reserves the right to change any circuitry or specifications without notice. IDT does not authorize or warrant any IDT product for use in life support devices or critical medical instruments.

#### **Revision History**

| Rev. | Originator | Issue Date | Description                                           | Page # |

|------|------------|------------|-------------------------------------------------------|--------|

| 0.1  | RDW        | 10/18/2011 | Initial Release                                       |        |

|      |            |            | 1. Updated General Description and Key Specifications |        |

|      |            |            | 2. Added Mark Spec                                    |        |

| Α    | RDW        | 12/12/2011 | 3. Moved to Final                                     | 1, 6   |

|      |            |            |                                                       |        |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Renesas Electronics: <u>6V31021NLGI</u> <u>6V31021NLGI8</u>